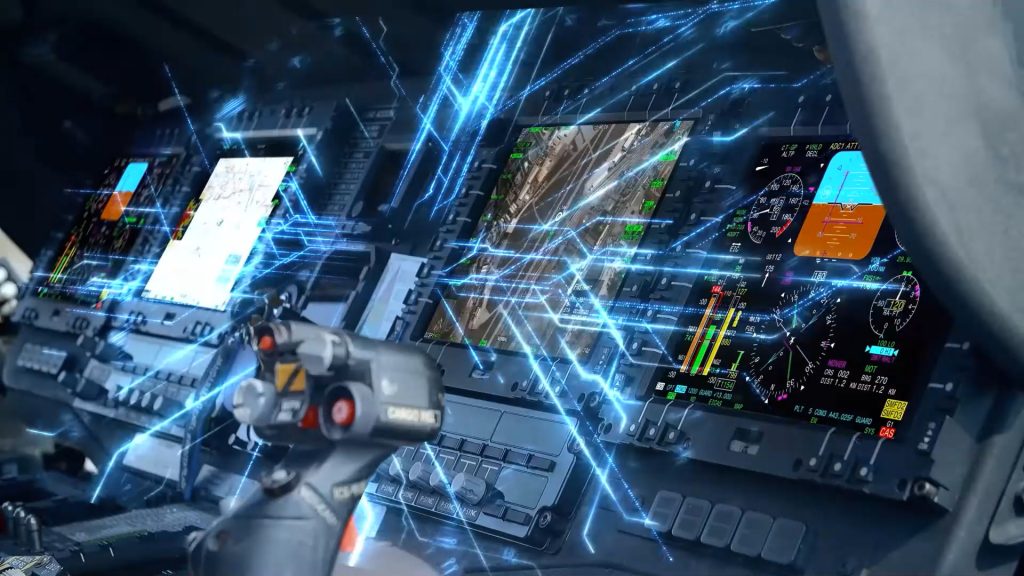

Development processes for hardware used in aviation.

DO-254 and AMC/AC 20-152A Training

DO-254 in conjuction with AMC 20-152A is the primary certification reference for airborne electronic hardware (AEH). Our training guides the attendees to understand how to develop and verify simple or complex hardware ensuring it is produced with an acceptable, traceable, and verifiable development process. BRNAvionics training presents this development assurance framework, shaped by authority (FAA/EASA) expectations, so that it can be understood and implemented by engineers, quality and managers alike.

Position in the Certification Ecosystem

DO-254 is the bridge between system engineering, safety analysis, and hardware development.

Hardware Life Cycle and Requirements

Full traceability from planning phase to hardware requirements.

Design and Verification Strategies

Modern approaches transforming hardware design decisions into certification evidence.

Circuit Board Design Certification

Partitioning, isolation, and safety principles in architecture. Certification impact of clocking, reset, and timing decisions.

FPGA Certification

HDL requirements, Synthesis, Place & Route, and Timing verification process within complex hardware scope.

Verification: The Core of DO-254

Review, analysis, and test methods; verification depth and audit scenarios varying by DAL levels.

Verification independence and audit perspective for DAL A hardware.

Establishing functional verification as certification evidence.

Audit and Auditor Perspective

Strategic preparation for FAA/EASA Stage of Involvement (SOI) audits.

Configuration Management

Change control, versioning, and traceable hardware baseline management.

Process Assurance (SQA)

Internal audit, finding management, and PR approach through real audit scenarios.

Advanced Hardware Topics

Modern challenges in hardware projects and methods to manage risk.

Training Methodology and Deliverables

We reinforce theoretical knowledge with application and audit scenarios.

Target Audience and Logistics

Design & Safety Engineers, Verification Teams, and Technical Leads.

2 or 3 day programs. On-site or interactive classroom options.

Are You Ready for Certification?

BRNAvionics training doesn’t just explain standards; it provides actionable, defensible knowledge for real projects.

Get in Touch

Get detailed information about training options that can be customized to your teams’ needs.